RISC Processor

RISC stands for Reduced Instruction Set Computer Processor, a microprocessor architecture with a simple collection and highly customized set of instructions. It is built to minimize the instruction execution time by optimizing and limiting the number of instructions. It means each instruction cycle requires only one clock cycle, and each cycle contains three parameters: fetch, decode and execute. The RISC processor is also used to perform various complex instructions by combining them into simpler ones. RISC chips require several transistors, making it cheaper to design and reduce the execution time for instruction.

Examples of RISC processors are SUN's SPARC, PowerPC, Microchip PIC processors, RISC-V.

Advantages of RISC Processor

- The RISC processor's performance is better due to the simple and limited number of the instruction set.

- It requires several transistors that make it cheaper to design.

- RISC allows the instruction to use free space on a microprocessor because of its simplicity.

- RISC processor is simpler than a CISC processor because of its simple and quick design, and it can complete its work in one clock cycle.

Disadvantages of RISC Processor

- The RISC processor's performance may vary according to the code executed because subsequent instructions may depend on the previous instruction for their execution in a cycle.

- Programmers and compilers often use complex instructions.

- RISC processors require very fast memory to save various instructions that require a large collection of cache memory to respond to the instruction in a short time.

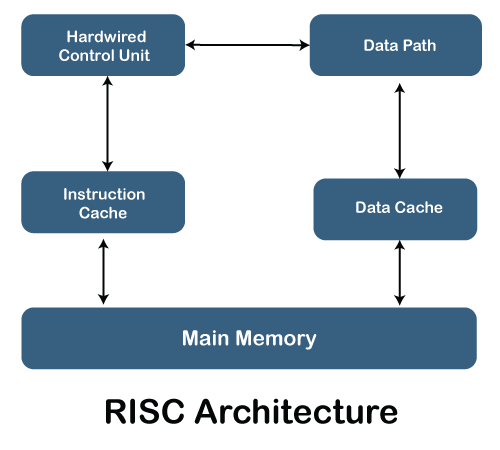

RISC Architecture

It is a highly customized set of instructions used in portable devices due to system reliability such as Apple iPod, mobiles/smartphones, Nintendo DS,

Features of RISC Processor

Some important features of RISC processors are:

- One cycle execution time: For executing each instruction in a computer, the RISC processors require one CPI (Clock per cycle). And each CPI includes the fetch, decode and execute method applied in computer instruction.

- Pipelining technique: The pipelining technique is used in the RISC processors to execute multiple parts or stages of instructions to perform more efficiently.

- A large number of registers: RISC processors are optimized with multiple registers that can be used to store instruction and quickly respond to the computer and minimize interaction with computer memory.

- It supports a simple addressing mode and fixed length of instruction for executing the pipeline.

- It uses LOAD and STORE instruction to access the memory location.

- Simple and limited instruction reduces the execution time of a process in a RISC.

No comments:

Post a Comment